앞의 글을 읽으시면 이해에 도움이 됩니다.

2022.11.11 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Data Hazard

[컴퓨터 구조] Data Hazard

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Hazard [컴퓨터 구조] Hazard 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Science/컴퓨

hi-guten-tag.tistory.com

2022.11.16 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Pipelined Control

[컴퓨터 구조] Pipelined Control

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.16 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Pipelined Datapath [컴퓨터 구조] Pipelined Datapath 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.01 -

hi-guten-tag.tistory.com

1. Data Hazard in ALU instructions

우선 ALU instruction에서 발생되는 Data hazard에 대해서 살펴봅시다.

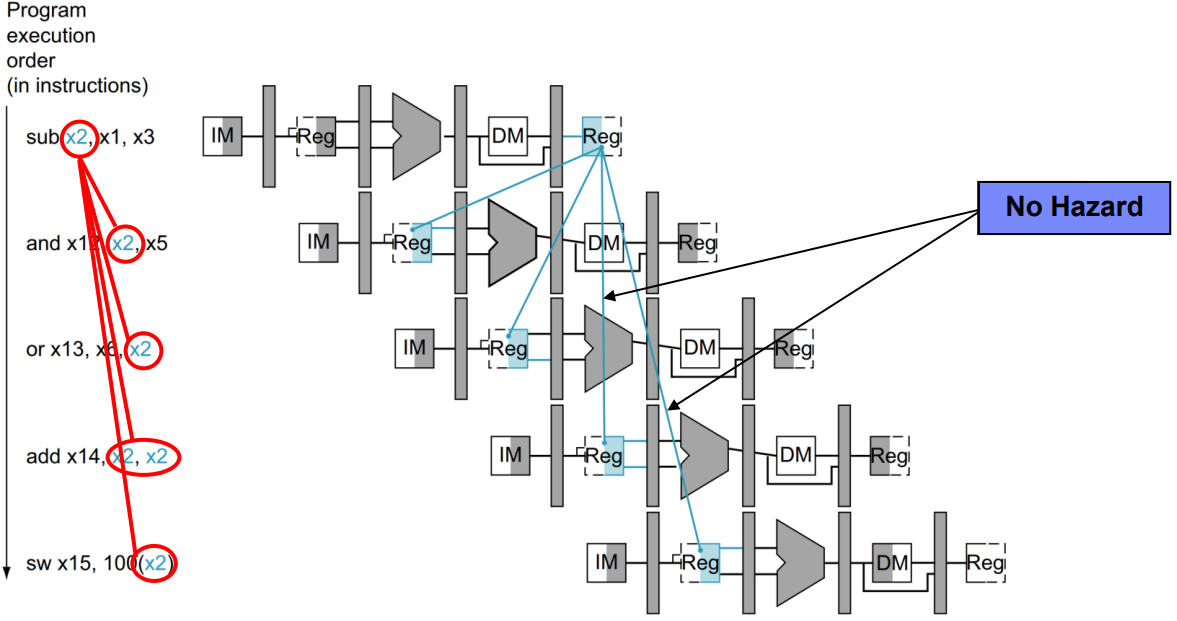

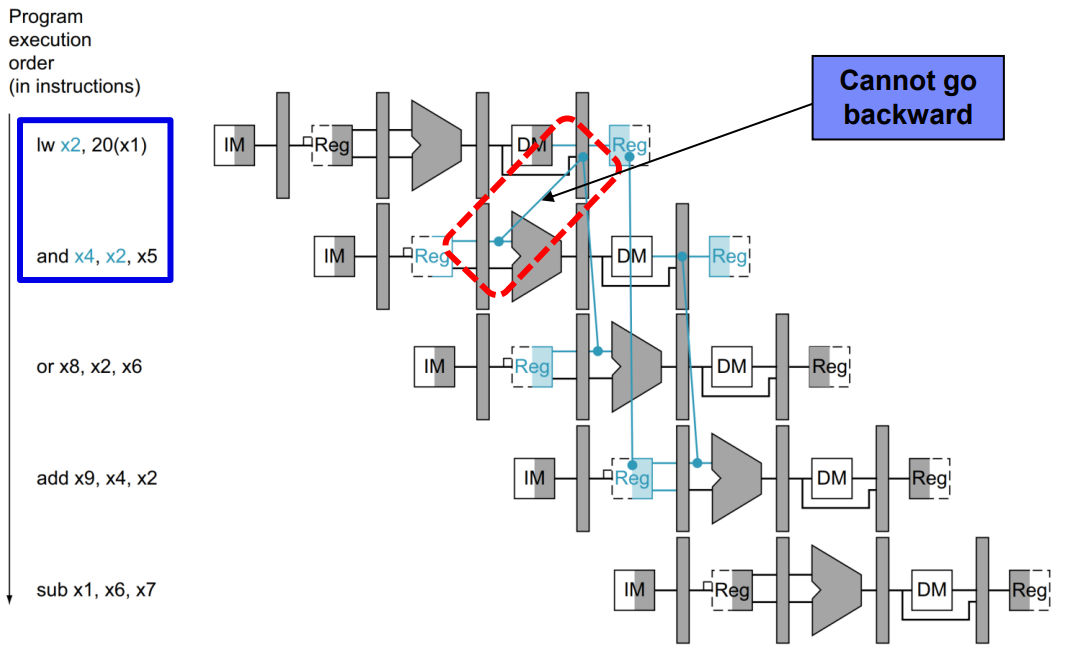

일반적인 Data hazard는 아래와 같은 그림에서 발생합니다.

dependence가 발생한 모습입니다.

그림에서 표시된 뒤에 있는 두 개의 ALU 연산에서는 Hazard가 발생하지 않습니다.

하지만 앞에 있는 두 개의 ALU 연산에는 Data Hazard가 발생하고 있습니다.

그렇다면 이를 Datapath에서는 어떻게 해결해야 할까요?

2. Detecting the Need to Forward

Data hazard 글에서 살펴봤듯이, Data hazard는 Forward 기법을 사용하여 해결합니다.

그렇다면 우선 Forward가 필요한 상황부터 검사해야 합니다.

조건들은 다음과 같습니다.

- EX/MEM Register RD = ID/EX Register RS1

- EX/MEM Register RD = ID/EX Register RS2

- MEM/WB Register RD = ID/EX Register RS1

- MEM/WB Register RD = ID/EX Register RS2

이러한 상황이 있을 때, Data hazard가 발생할 수 있습니다.

위 두 개의 경우는 바로 이전의 stage에서 dependency가 발생한 상태이므로 EX/MEM에서 forward를 해야 하고,

아래의 두 개는 이전 이전의 stage에서 dependency가 발생한 상태이므로 MEM/WB에서 forward를 해야 합니다.

여기까지가 Dependency를 검사하는 과정입니다.

하지만 만약 Register에 Write를 하지 않는다면 아무 의미가 없겠죠?

따라서 아래의 검사도 추가로 진행합니다.

- EX/MEM RegWrite, MEM/WB RegWrite

Register에 실질적으로 Write를 하는지 검사합니다.

또한,

- EX/MEM Register RD != 0

- MEM/WB Register RD != 0

만약 Rd가 0이라면 zero register에 넣는 것이므로 아무 의미가 없기 때문에 해당 조건도 검사합니다.

따라서 dependency가 발생했는지 확인하는 조건 하나, 실제로 데이터가 Register에 입력되는지 확인하는 조건 둘

총 3개의 조건을 만족해야 비로소 Forwarding을 합니다.

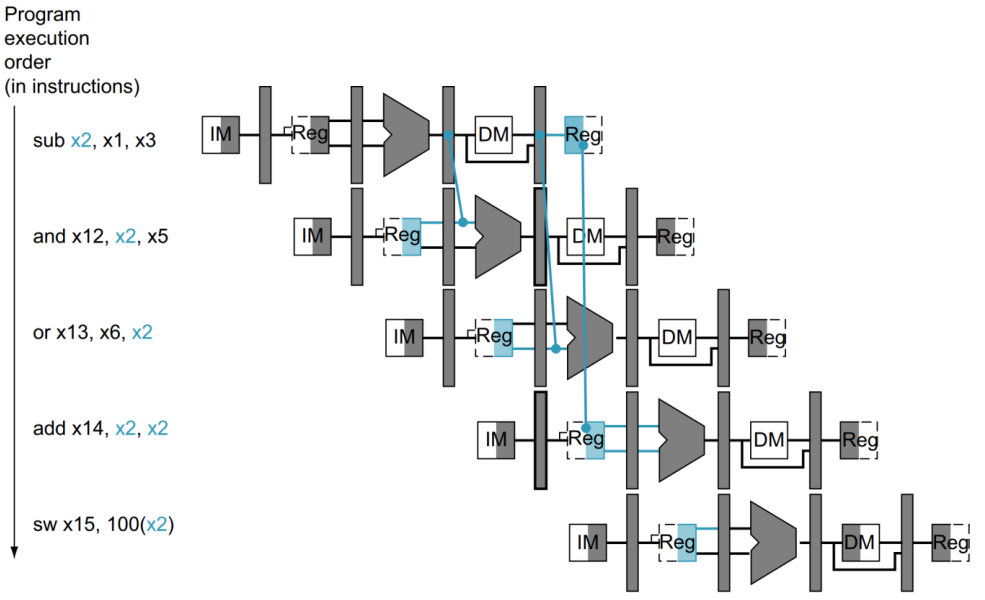

Forwarding을 한다면 아래의 그림과 같습니다.

여기서 주의해야 할 점이 R-Type 같은 경우에는 EX/MEM의 값과 MEM/WB의 값이 같다는 점입니다.

(물론 완벽히 같은건 아님. 설명하자면 복잡하므로 설명이 필요하다면 댓글을 남겨주세요.)

그렇기 때문에 EX/MEM의 값이 ID/EX로 Forward를 할 수 있는 것입니다.

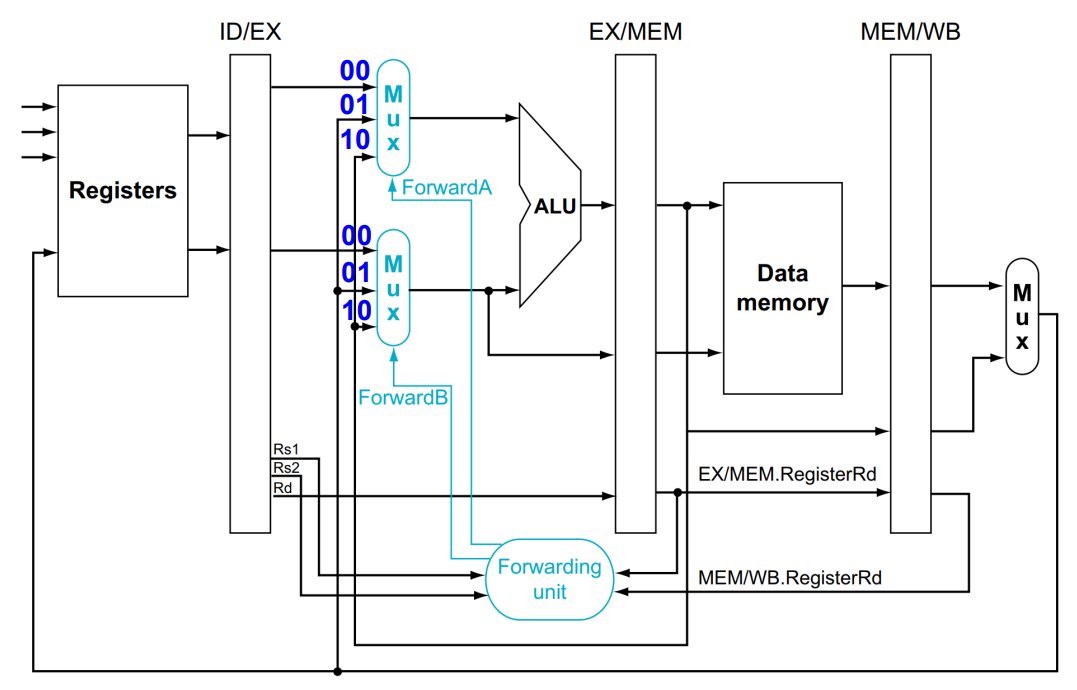

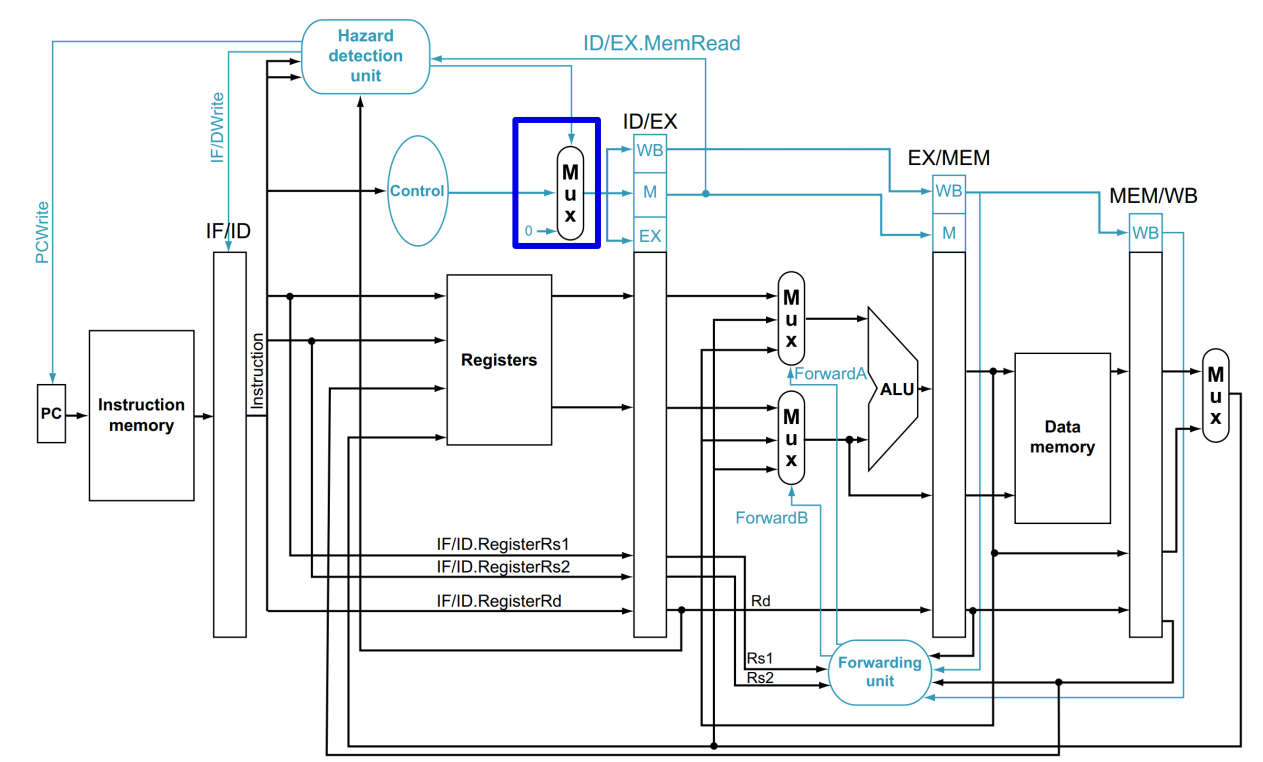

이제 Datapath를 보도록 합시다.

Datapath에 Forwarding Unit이 추가되었습니다.

해당 Unit은 앞서 말한 조건을 확인하고, 멀티플렉서를 통해 어떤 값을 사용할지 신호를 보냅니다.

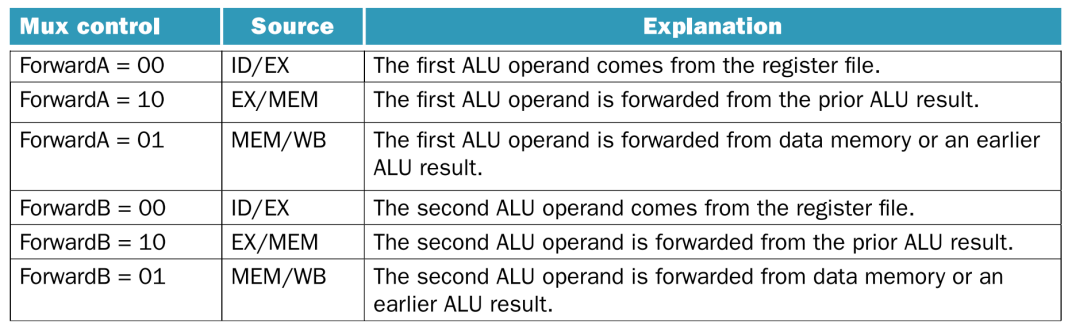

이때 Forwarding Unit이 보내는 신호는 위와 같습니다.

10은 EX/MEM에서 값을 보내고, 01은 MEM/WB에서 값을 보냅니다.

이때 Forward A인지, Forward B인지도 Unit에서 결정합니다.

3. Load-Use Hazard

앞선 글에서 Load-Use hazard는 하드웨어가 해결할 수 없다고 설명드렸습니다.

따라서 컴파일러가 이를 해결해줘야 하는데, 그럼에도 불구하고 Load-Use Hazard가 발생하면 어떻게 되는지 살펴봅시다.

Load-Use 같은 경우에는 Memory에서 값을 읽기 때문에 Forwarding이 불가능합니다.

정상적인 값이 MEM/WB Register에 들어가 있기 때문입니다.

이런 경우에는 어쩔 수 없이 pipeline stall을 해야 합니다.

그렇다면 최대한 빨리 stall을 하는 것이 손실을 줄일 수 있겠죠?

조건을 알아봅시다.

- ID/EX MemRead = 1

- ID/EX Register RD = IF/ID Register RS 1

- ID/EX Register RD = IF/ID Register RS 2

아예 ID 단계에서 해당 조건을 만족한다면 stall을 진행합니다.

이때 stall을 하기 위해서는 두 가지의 행동이 필요합니다.

- PC의 업데이트를 막고, IF/ID pipeline Register의 업데이트를 막는다.

- ID/EX Register의 값을 모두 0으로 만든다.

우선 PC, IF/ID Register의 업데이트를 막아야 합니다.

다만 그렇다해도, ID Stage에서는 Instruction Decode를 진행하고, IF Stage에서는 다시 한번 명령어를 반입합니다.

또한 ID/EX Register의 값을 0으로 만드는데, 이렇게 해야만 뒷 단계에서는 아무것도 하지 않기 때문입니다.

따라서 EX, MEM, WB stage에서는 아무것도 하지 않습니다.

왜냐면 Data Hazard가 발생하면, 기존의 Register 값은 아무런 쓸모가 없기 때문입니다.

Datapath의 그림을 한 번 봅시다.

IF/ID Register에서 Hazard Detection Unit으로 신호를 보내면, 해당 Unit에서 Stall을 결정합니다.

만약 stall을 하기로 결정했다면, 첫 번째로 PC의 update를 막고, 두 번째로 ID/EX Register를 모두 0으로 초기화합니다.

네모가 쳐져있는 멀티플렉서에서는 Control 신호를 보낼 것인가, 아니면 0으로 초기화 할 것인가를 결정합니다.

만약 PCWrite 신호가 0이라면 Update를 하지 않습니다.

여기까지 Data Hazard를 막기 위한 혹은 손실을 최소화하기 위한 Datapath에 대한 글입니다.

다음은 또 다른 Hazard인 Control Hazard를 막는 Datapath에 대해 소개하도록 하겠습니다.

2022.11.16 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Control Hazard in Pipelined Datapath

[컴퓨터 구조] Control Hazard in Pipelined Datapath

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.11 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Control Hazard [컴퓨터 구조] Control Hazard 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Compute

hi-guten-tag.tistory.com

감사합니다.

지적 환영합니다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] RISC-V Simulator (0) | 2022.11.22 |

|---|---|

| [컴퓨터 구조] Control Hazard in Pipelined Datapath (0) | 2022.11.16 |

| [컴퓨터 구조] Pipelined Control (0) | 2022.11.16 |

| [컴퓨터 구조] Pipelined Datapath (2) | 2022.11.16 |

| [컴퓨터 구조] Control Hazard (9) | 2022.11.11 |