앞의 글을 읽으시면 이해에 도움이 됩니다.

2022.11.16 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Pipelined Datapath

[컴퓨터 구조] Pipelined Datapath

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.01 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Basic Implementation of the RISC-V (RISC-V의 기본적인 구현) [컴퓨터 구조] Basic Implementation of the RISC-V (RISC-V

hi-guten-tag.tistory.com

1. Pipelined Control

이제 기본적인 DataPath는 보았으니, 살을 붙입시다.

처음은 Control 신호입니다.

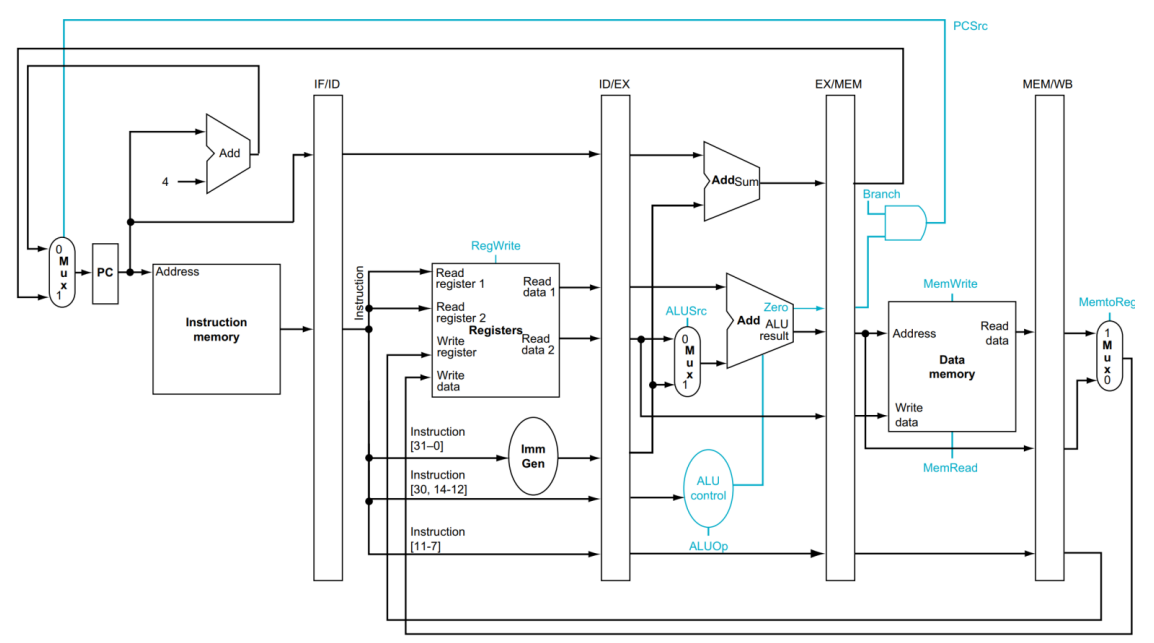

그림을 보면, Control Path가 추가되었습니다.

다만 여기에 매번 수행되는 Pipeline Regsiter의 write signal과, PC에 대한 control은 없습니다.

이는 매 Clock Cycle 마다 수행되므로, 따로 표기하지 않습니다.

MEM Stage를 보시면 Branch를 하는데, 앞선 글에서 설명했듯이, Branch는 MEM Stage에서 발생합니다.

2. Control Lines

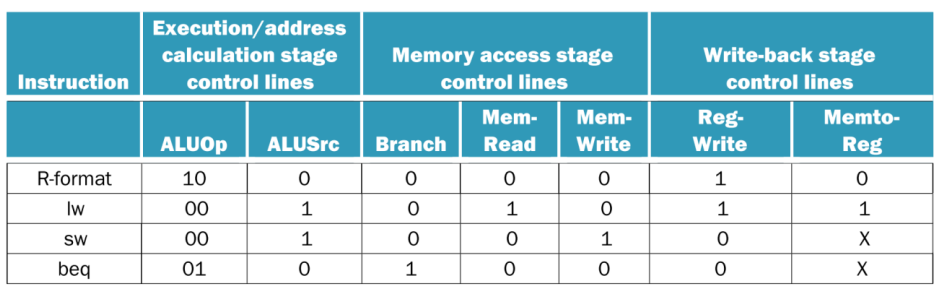

이때 control 값이 어떻게 되는지 알기 위해서 각 stage 별로 어떤 control 신호가 입력되는지 알아보겠습니다.

- IF : Nothing Special

- ID : Nothing Special

- EX : ALUOp, ALUSrc

- MEM : MemRead, MemWrite, Branch

- WB : MemtoReg, RegWrite

입니다.

ALUOp는 어떤 연산을 수행할 것인지에 대한 값

ALUSrc는 Imm를 사용할 것이냐에 대한 값입니다. 만약 ALUSrc가 0이라면 Register 2의 값을 사용합니다.

MemtoReg는 Memory의 값을 Register에 쓸 것이냐에 대한 값입니다. 만약 값이 0이라면 ALU의 연산 결과를 Register에 입력합니다.

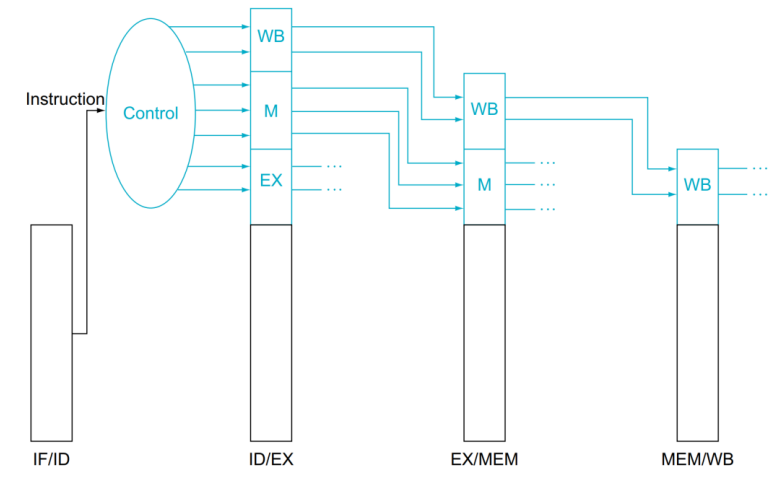

하지만 Control은 5개가 아니기 때문에, ID에서 생성된 Control 신호가 다음 Stage에도 계속해서 흘러가야 합니다.

그렇지 않다면 Control은 매번 각 Stage 별로 신호를 생성해야 합니다.

매우 비효율적이기 때문에 Control 신호 또한 Pipeline Register를 통해서 흘러서 다음 Stage에 가야 합니다.

3. Control Lines for the Final Three Stages

Pipeline Register를 확장하여, 이후 stage의 control 신호가 갈 수 있도록 만듭니다.

위에서 설명드렸다시피, EX에서 필요한 Control 신호는 2개, MEM은 3개, WB는 2개입니다.

따라서 ID/EX Register는 7개의 control line이 추가적으로 필요하고, EX/MEM은 5개, MEM/WB는 2개가 추가적으로 필요합니다.

Control 신호는 ID Stage, 즉 Instruction Decode에서 발생하기 때문에, ID Stage 이후로만 Control 신호가 흐릅니다.

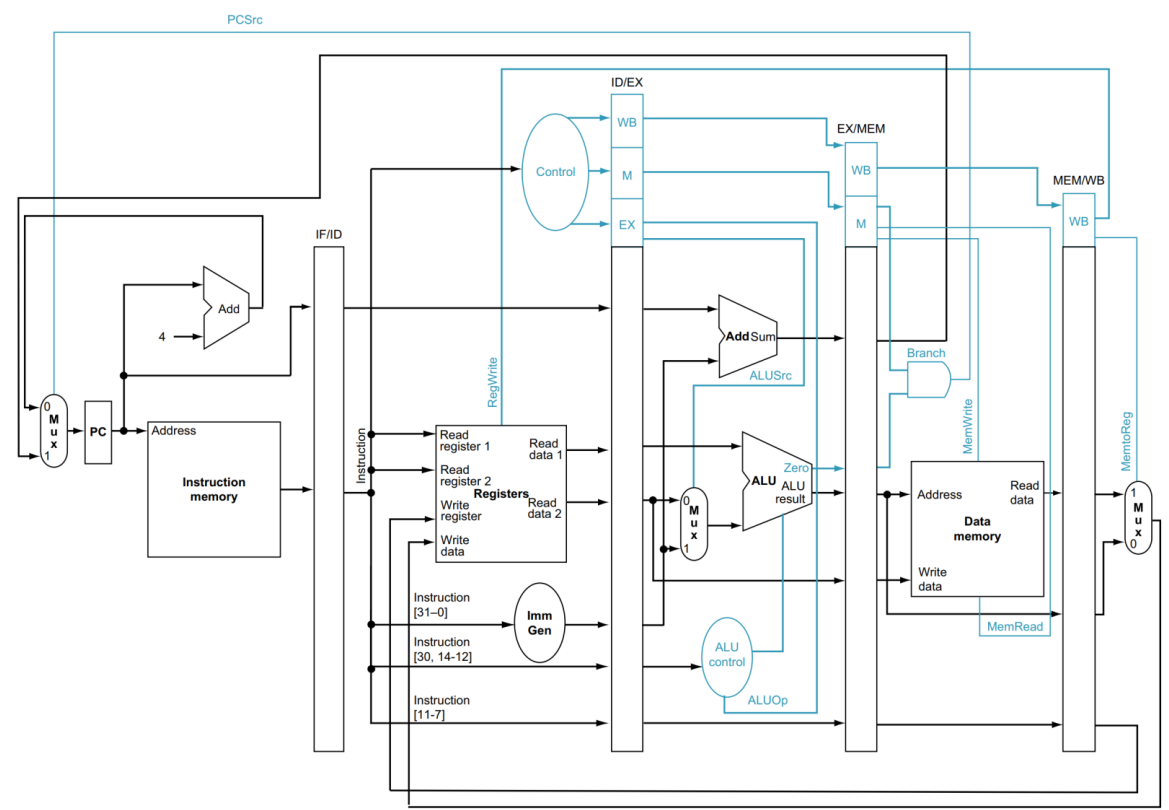

따라서 Control Signal을 추가한 Pipelined Datapath는 다음과 같습니다.

따라서 WB stage에서 RegWrite Control Signal은 앞으로 진행되어, ID stage에 도달하게 됩니다.

보시다시피, ALU의 Zero Signal은 EX stage에서 나옵니다.

다만 stage의 끝에서 결과가 도출되기 때문에, 한 stage 내에서 zero로 무언가를 하기에는 너무 늦은 상태입니다.

따라서 beq 같은 branch instruction이 MEM stage에서 실행됩니다.

여기까지 Control Signal을 보장하기 위한 Datapath에 대해서 살펴봤습니다.

다음 글에서는 Pipeline의 Hazard를 막기 위한 Datapath 기법들에 대해 살펴보겠습니다.

2022.11.16 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Data Hazard in Pipelined Datapath

[컴퓨터 구조] Data Hazard in Pipelined Datapath

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.11 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Data Hazard [컴퓨터 구조] Data Hazard 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Scie

hi-guten-tag.tistory.com

감사합니다.

지적 환영합니다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Control Hazard in Pipelined Datapath (0) | 2022.11.16 |

|---|---|

| [컴퓨터 구조] Data Hazard in Pipelined Datapath (0) | 2022.11.16 |

| [컴퓨터 구조] Pipelined Datapath (2) | 2022.11.16 |

| [컴퓨터 구조] Control Hazard (9) | 2022.11.11 |

| [컴퓨터 구조] Data Hazard (2) | 2022.11.11 |