앞의 글을 읽으시면 이해에 도움이 됩니다.

2022.11.10 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Hazard

[컴퓨터 구조] Hazard

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Pipelining [컴퓨터 구조] Pipelining 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.01 - [Computer Scienc

hi-guten-tag.tistory.com

목차

1. Data Hazard

2. 해결법

3. Load-Use Data Hazard

1. Data Hazard

Data Hazard는 어떤 stage가 다른 stage가 끝날 때까지 기다려야 하기 때문에 발생합니다.

즉 instruction이 이전의 instruction에 대해서 dependency를 가지고 있기 때문에 발생합니다.

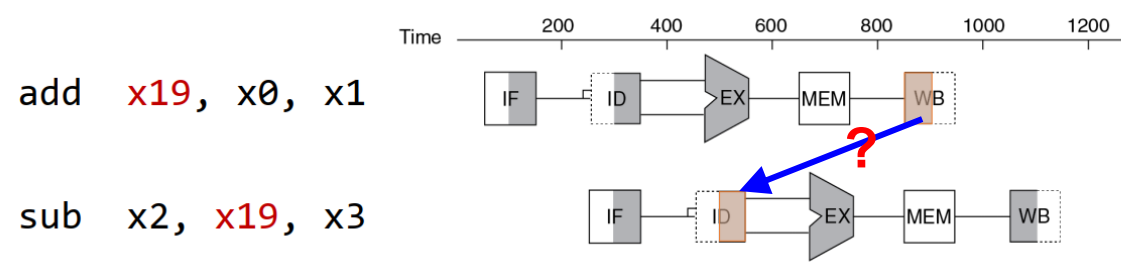

(참고로 오른쪽 회색은 read, 왼쪽 회색은 write입니다.)

위의 그림을 보시면 x19에 WB가 되기 전에, Sub instruction가 x19에 참조를 하는 모습입니다.

덧셈 결과를 x19에 저장해야 하고, 그 저장된 값을 바탕으로 sub 해야 하는데,

저장되기 전인 x19를 read 하려는 모습입니다.

sub instruction이 앞선 add instruction에 의존하고 있습니다.

이것을 Data Hazard라고 합니다.

이를 해결하기 위해서는 3 clock cycle만큼 stall 해야 하므로, 그만큼 손해가 발생하게 됩니다.

그렇다면 stall 하지도 않고도, Data Hazard를 막는 방법이 무엇이 있을까요?

2. 해결법

사실 이러한 문제는 컴파일러가 대부분 해결해줍니다.

dependency 문제가 발생할 것 같다면, 컴파일러는 중간에 x19를 참조하지 않는 명령어를 넣음으로써 이를 해결합니다.

하지만 이러한 dependency는 너무 자주 발생하고, 만약에 긴 명령어가 있을 때 컴파일러가 해결하지 못한다면 손해가 너무 큽니다.

(하나의 명령어가 100 stage로 구성될 때, 만약 90번째 명령어에서 dependency가 발생한다면, 최소한 91번 stall 해야 함.)

이러한 문제는 하드웨어에서 발생하는 문제기 때문에, 소프트웨어로 해결하기에는 충분하지 않아 보입니다.

따라서 하드웨어적으로 문제를 해결하는데, 이것이 바로 Forwarding입니다.

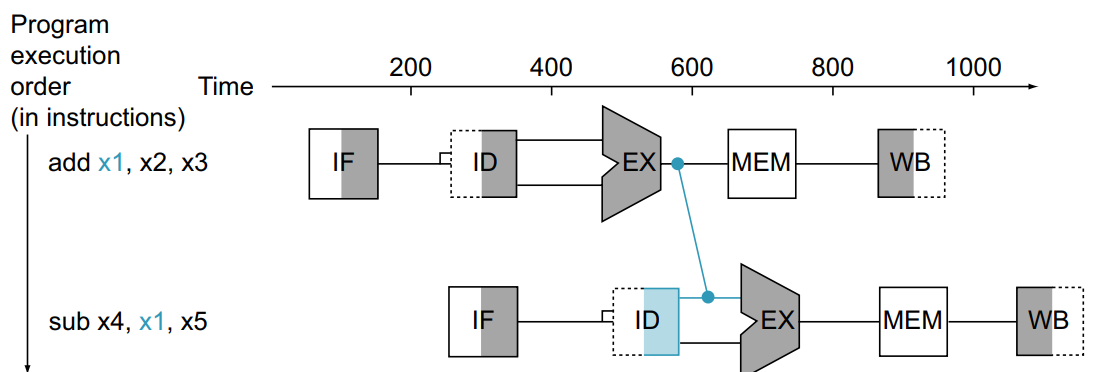

Forwarding은 Data Hazard를 해결하기 위한 기법입니다.

ALU(EX 단계)에서 add를 계산하고 난 후에 곧바로 sub에게 결과를 제공합니다.

쉽게 그림으로 표현하면 다음과 같습니다.

어차피 add기 때문에 memory는 참조할 필요가 없습니다.

따라서 곧바로 다음 명령어에게 값을 전달하면 해결할 수 있습니다.

다만 해당 그림은 시간축을 따라 표현한 것이기에, 실제로는 EX에서 나온 선이 곧바로 ID와 EX 사이로 들어간다고 보시면 됩니다.

아무튼 Forwarding은 Destination Stage가 Source Stage보다 늦게 있어야 가능합니다.

MEM에서 나온 값이 ID/EX 사이로 들어갈 수는 없습니다. 과거로 갈 수 없기 때문입니다.

이렇나 Forwarding을 통해서 register 간의 Data Hazard는 해결했습니다.

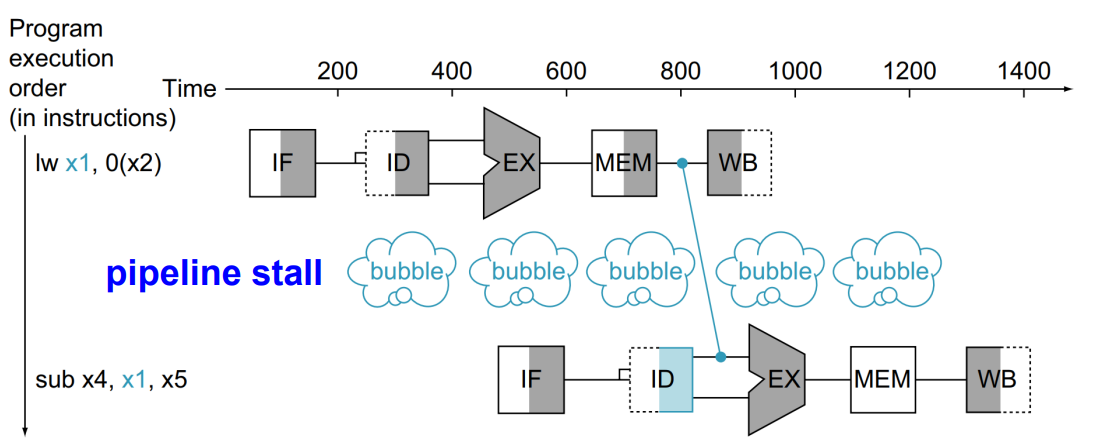

하지만 만약에 MEM에서 나온 값을 바로 뒤에서 참조해야 한다면 어떻게 될까요?

3. Load-Use Data Hazard

MEM에서 나온 값은 ID/EX 사이로 들어갈 수 없습니다.

왜냐면 MEM에서 나온 값은 시간상으로 ID/EX보다 먼저 수행된 값이기 때문입니다.

따라서 이런 경우에는 pipeline stall을 해야 할 것 같습니다.

그러므로 load-use data hazard가 발생하면 stall을 해야 합니다...

그나마 forwarding을 사용해서 1 clock cycle만 delay 됐네요.

하지만 이것도 해결할 수 있지 않을까요?

2번 목차에서 컴파일러가 중간에 쓸데없는 명령어를 넣음으로써 대부분의 data hazard는 해결한다고 했습니다.

그렇다면 여기서도 컴파일러가 어떻게 해결해주지 않을까요?

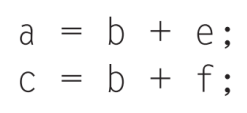

컴파일러는 pipeline stall을 막기 위하여 코드를 재구성합니다.

이런 명령어가 있다고 가정해봅시다.

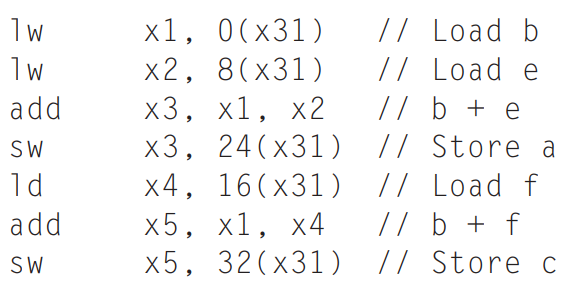

그렇다면 어셈블리어는 다음과 같습니다.

이때 lw 다음에 바로 add가 나오므로, data hazard가 발생합니다.

따라서 1 clock cycle만큼 stall 해야겠네요.

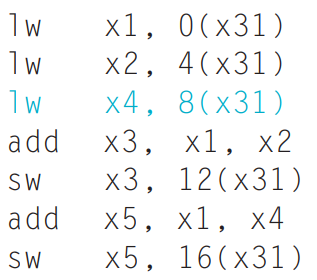

하지만 컴파일러는 이 코드를 재구성하여 문제를 해결합니다.

아래의 lw를 위로 끌어올림으로써 문제를 해결합니다.

이렇게 하면 data hazard가 발생하지 않아서, stall, pipeline bubble을 할 필요가 없습니다.

따라서 기존의 버전보다 2 cycle 적게 사용합니다.

하드웨어적으로 해결할 수 없으니, 소프트웨어적으로 해결하는 모습입니다.

만약 R-Type만 있다면 컴파일러가 이런 노력을 안 해도 되지만, Load를 사용한다면 어쩔 수 없이 컴파일러가 이를 해결해야 합니다.

다음 글에서는 Control Hazard에 대해서 알아보겠습니다.

2022.11.11 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Control Hazard

[컴퓨터 구조] Control Hazard

앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Science/컴퓨터 구조] - [컴퓨터 구조] Hazard [컴퓨터 구조] Hazard 앞의 글을 읽으시면 이해에 도움이 됩니다. 2022.11.10 - [Computer Science/컴퓨

hi-guten-tag.tistory.com

감사합니다.

지적 환영합니다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] Pipelined Datapath (2) | 2022.11.16 |

|---|---|

| [컴퓨터 구조] Control Hazard (9) | 2022.11.11 |

| [컴퓨터 구조] Structural Hazard (0) | 2022.11.10 |

| [컴퓨터 구조] Hazard (0) | 2022.11.10 |

| [컴퓨터 구조] Pipelining (0) | 2022.11.10 |